Specification:

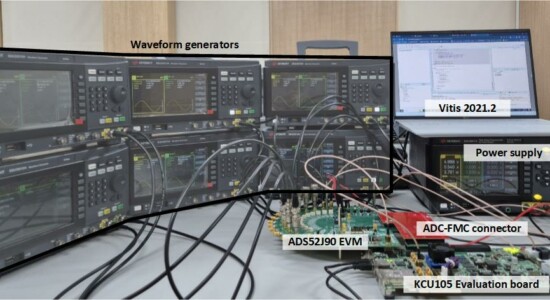

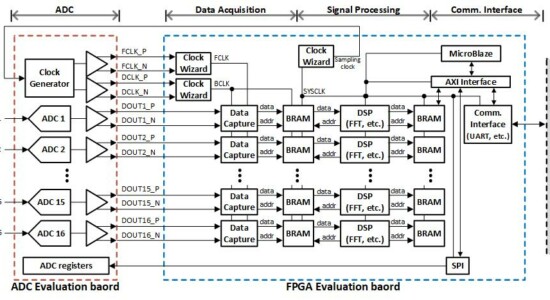

- FPGA : Xilinx Kintex UltraScale KCU105 Evaluation Board (KU040 FPGA)

- ADC : TI ADS5290 EVM (ADS5290 ADC)

- # of Ch. : 16

- Sampling Freq. : Max. 100MSPS

Folder configuration:

- Block design : design_1.bd

- HDL source : DataCapt.v / D_SHIFTREG.v / D_CNT.v / FFT_input.v / CORDIC_input.v / CORDIC_output.v / REG_RST.v

- Constraints : const.xdc

- S/W header : platform_config.h / platform.h

- S/W source : main.c / echo.c / i2c_access.c / iic_phyreset.c / platform.c / platform_mb.c / platform_ppc.c / platform_zynq.c / platform_zynqmp.c / stp.c / si5324.c

How to get source code of the platform